# Attackboard: A Novel Dependency-Aware Traffic Generator for Exploring NoC Design Space

Yoshi Shih-Chieh Huang, Yu-Chi Chang, Tsung-Chan Tsai, Yuan-Ying Chang and Chung-Ta King Department of Computer Science, National Tsing Hua University, Hsinchu, Taiwan

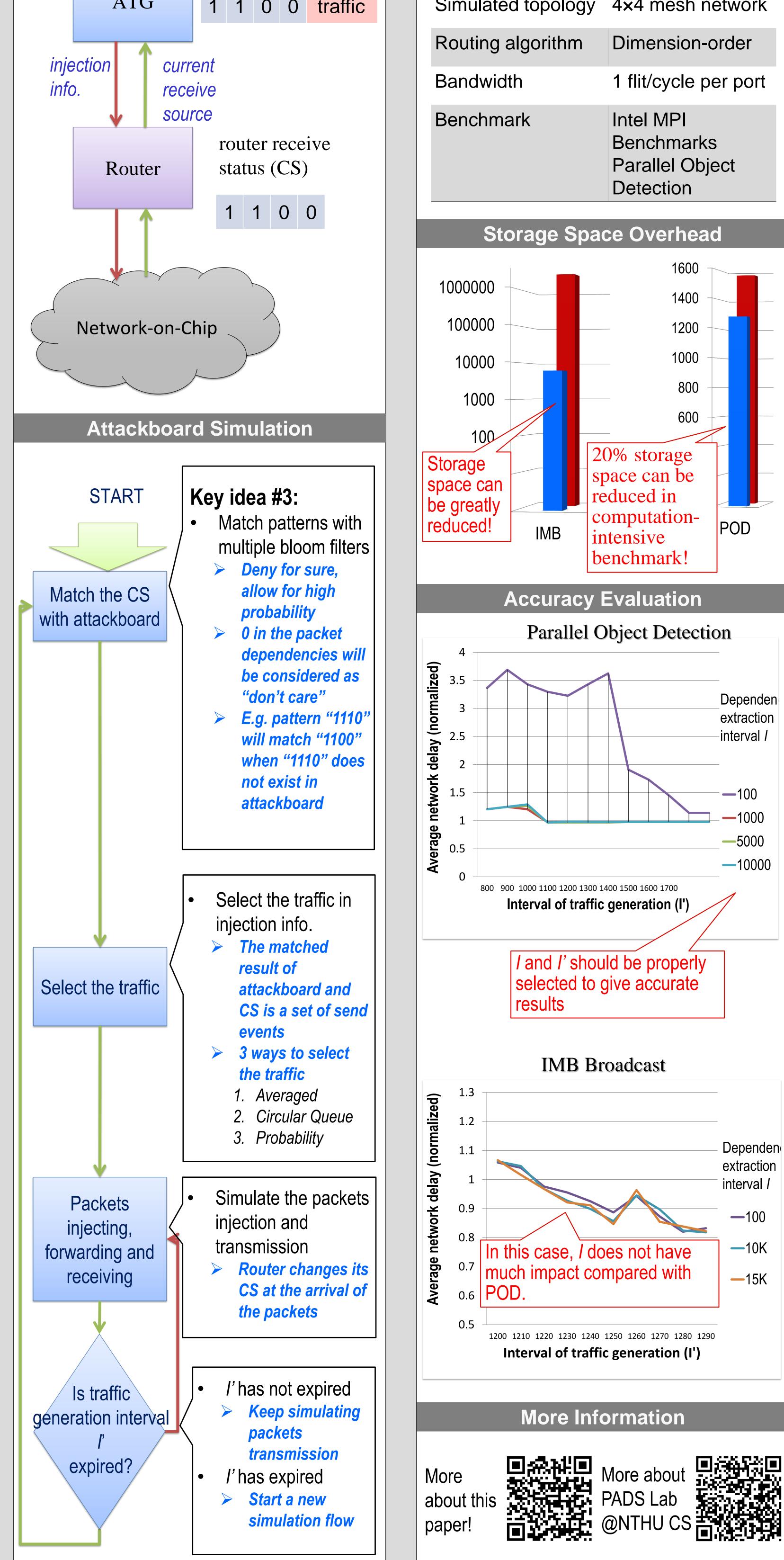

| Motivation                                                                 | Rebuild The State Machine                            | Overview of Attackboard                | Evaluation Setup                          |  |

|----------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------|-------------------------------------------|--|

|                                                                            | Attackboard uses small tables to represent the state |                                        | Emulate ATG on Tilera TILE64              |  |

| Trace-driven simulation is simple and fast for exploring NoC design space. |                                                      | Attackboard Traffic Generator<br>(ATG) | Native processor Tilera TILE64<br>element |  |

| For the consideration of accuracy, traces with packet dependencies is      | machines                                             | attackboard                            | Native processor 700 Mhz<br>frequency     |  |

| necessarv.                                                                 | How to do?                                           | ATG 1 1 0 0 troffic                    | Simulated topology /x/ mesh network       |  |

noocoodiy.

However, these trace logs can be very complicated and require large storage space!

The BIG problem is size, while the conventional trace compression mechanism is not a good solution for reducing the size of traces while maintaining accuracy.

**Key Question**

## How to reduce size of traces while maintaining accuracy?

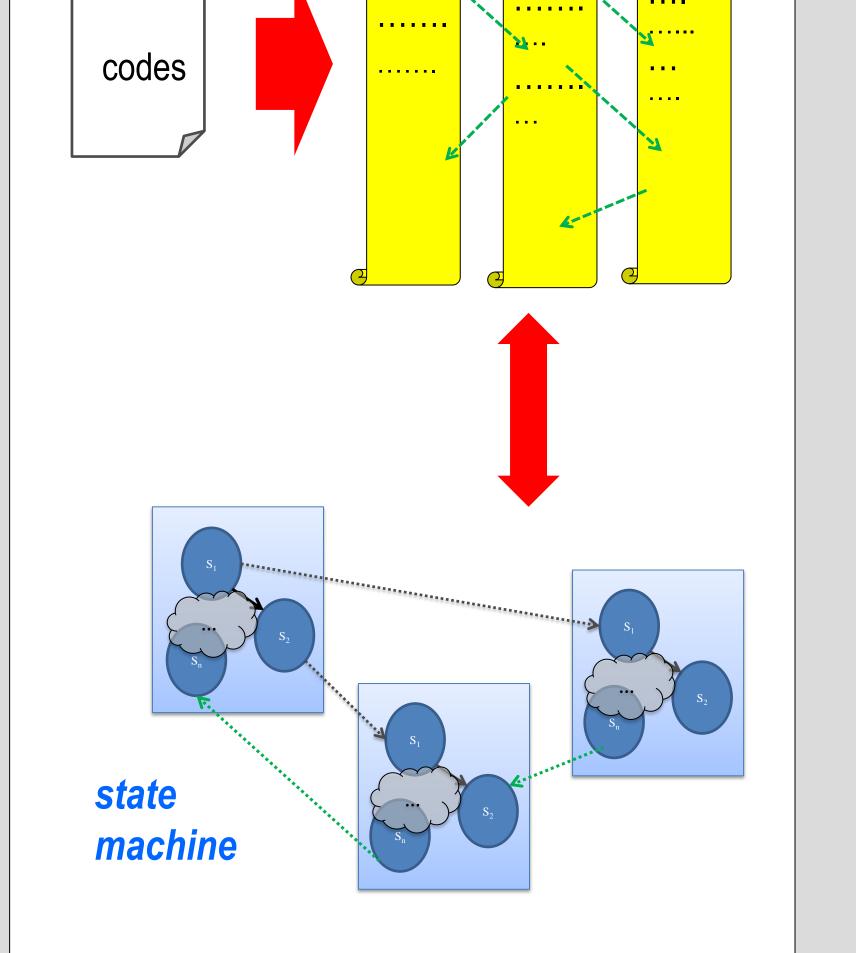

**Domain:** NoC design space exploration

#### How to do?

- State transitions are triggered by arrivals of packets

- > Leverage packet dependency info. in traces

- Focus on patterns of received packets

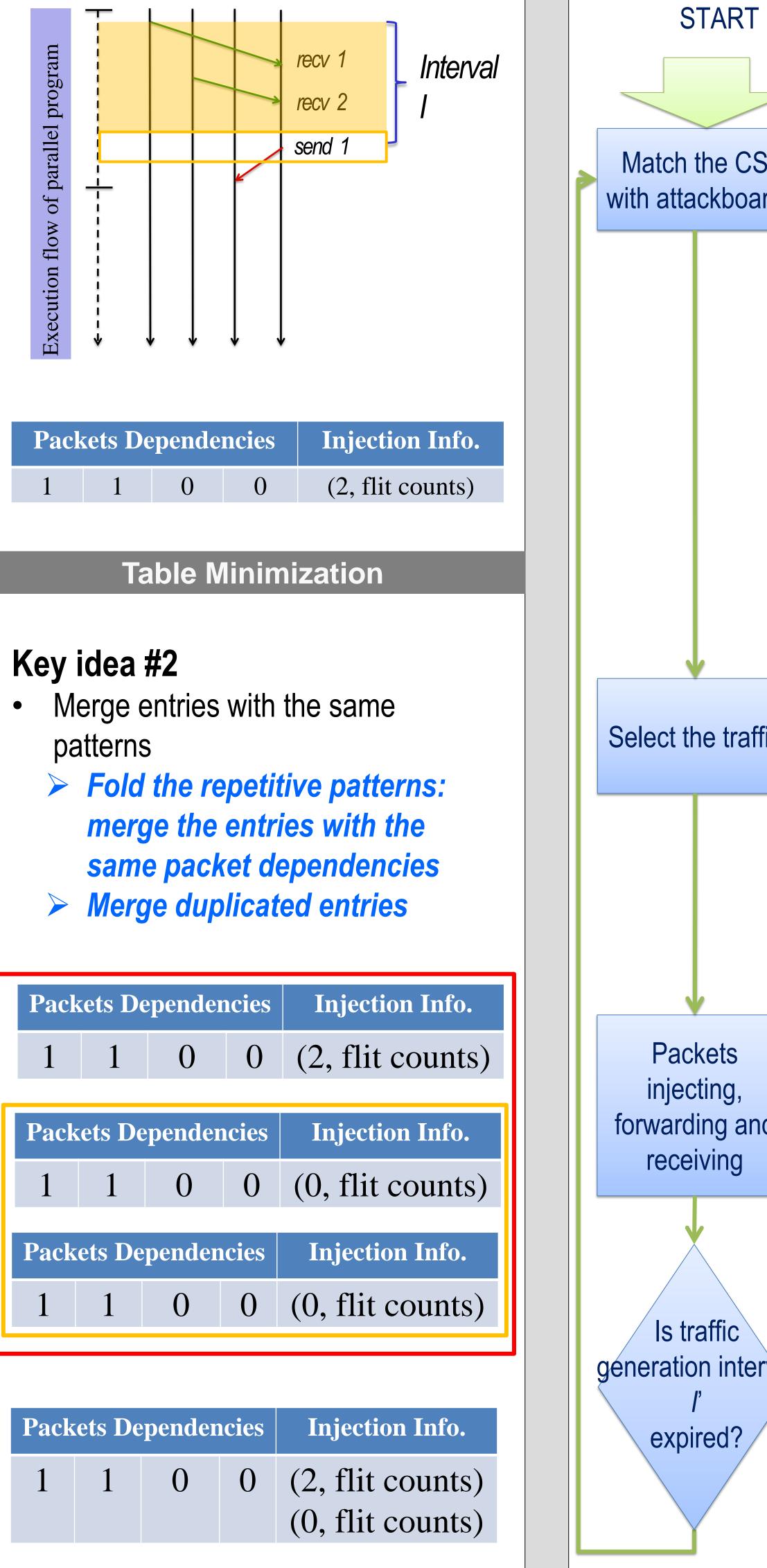

### Key idea #1

- Time-driven to pattern-driven

- > Use packet arrival patterns to replace the time sequencing

- > Inject packets by the sequencing of states

PE0 PE1 PE2 PE3

|                        | Simulated topology                                                                           |               | 4x4 mesh network                                                                                                             |     |  |

|------------------------|----------------------------------------------------------------------------------------------|---------------|------------------------------------------------------------------------------------------------------------------------------|-----|--|

|                        | Routing algorithm                                                                            |               | Dimension-order                                                                                                              |     |  |

|                        | Bandwidth                                                                                    |               | 1 flit/cycle per port                                                                                                        |     |  |

|                        | Benchmark                                                                                    |               | Intel MPI<br>Benchmarks<br>Parallel Object<br>Detection                                                                      |     |  |

| Storage Space Overhead |                                                                                              |               |                                                                                                                              |     |  |

|                        | 1000000<br>100000<br>10000<br>1000<br>1000<br>Storage<br>space can<br>be greatly<br>reduced! | IMB SJ<br>IMB | 1600<br>1400<br>1200<br>1000<br>800<br>600<br>0% storage<br>pace can be<br>educed in<br>omputation-<br>itensive<br>enchmark! | POD |  |

#### **Proposal:** A novel pattern-driven simulation mechanism

#### **Key Insights**

- Each PE has its own BIG trace for NoC operations

- Each BIG trace is actually a log of the execution of the corresponding *State Machine*

**10KB codes may** result in more than 1GB traces!

**1GB trace** logs

www.PosterPresentations.c