#### CS4101 嵌入式系統概論

# **Timers and Clocks**

Prof. Chung-Ta King Department of Computer Science National Tsing Hua University, Taiwan

Materials from *MSP430 Microcontroller Basics*, John H. Davies, Newnes, 2008

# **Recall the Container Thermometer**

- Container thermometer: monitor the temperature of the interior of a container

- Monitor the temperature every 5 minutes

- Flash LED alarm at 1 Hz

- If the temperature rises above a threshold, flash the LED alarm at 3 Hz and notify backend server

- If the temperature drops below a threshold, return the LED alarm to normal and notify the server

#### Need to know exact time!

Many embedded systems are used to control things based on time or that have time constraints

- Traffic light controller

- Power meter

- Pacemaker (心跳節律器)

- Subway collision avoidance system

- Airbag

#### How to track real (wall clock) time?

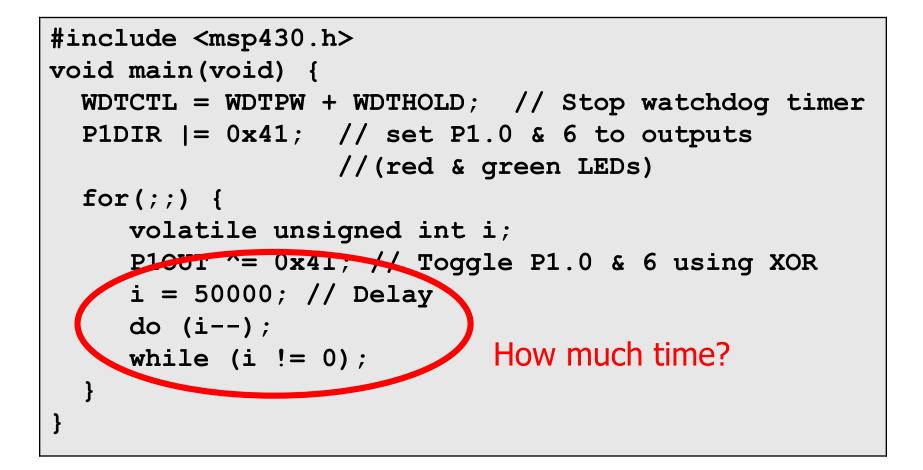

#### **Recall First MSP430 Program**

## **Problems Regarding Time**

- Using software delay loops

- Waste of processor because it is not available for other operations

- Difficult to translate into actual time

- Given a time for the delay, difficult to translate into number of iterations

- The delays are unpredictable, e.g., compiler optimization, interrupts

#### We need an independent reference of time!

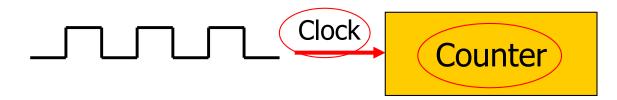

# **Reference of Time**

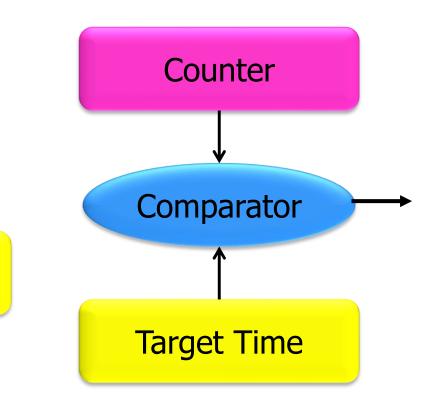

The simplest hardware to provide a reference of time is a counter that counts every fixed unit of time → timer

- The actual time can be obtained by multiplying the counter with the clock interval time

- $\rightarrow$  The accuracy and stability of the clock is critical

#### Where to put the timers?

#### Make Timer an IO Device!

National Tsing Hua University

#### **Timers Being IO Devices**

Have internal registers with addresses in the memory space for the CPU to access

### **Typical Registers in a Timer**

- The counter itself

- Target for counting

- Control settings

- Others: clock source selection, flags

Control

- Basic concepts of timers

- MSP430 timers

- An example of using MSP430 Timer\_A

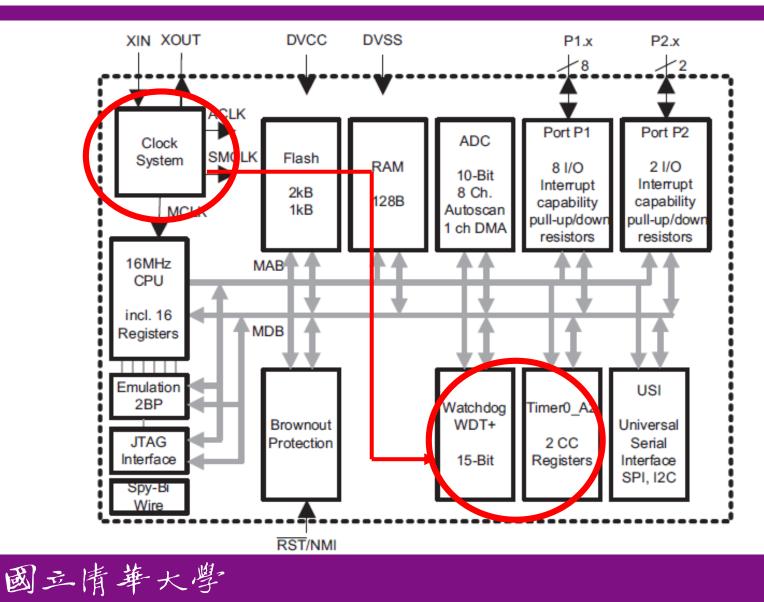

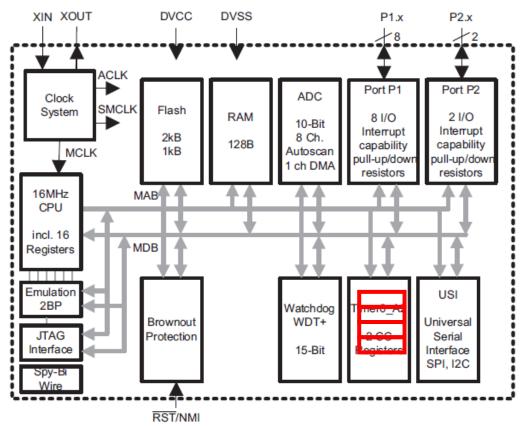

- Clocks in MSP430

Contain several timers, including:

- Timer\_A

- A 16-bit counter, TAR, with three capture/compare registers.

- Watchdog timer

- Count up and reset MSP430 when it reaches its limit

- The code must keep clearing the counter before the limit is reached to prevent a reset

- Protect system against failure of software, such as unintended, infinite loops

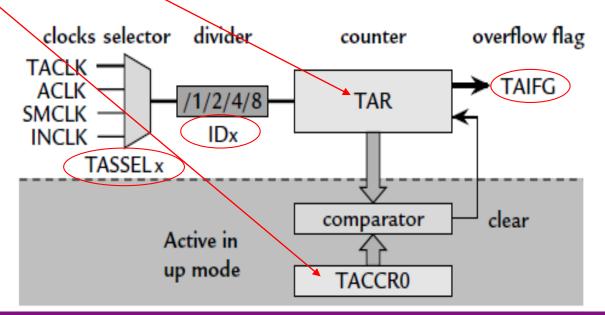

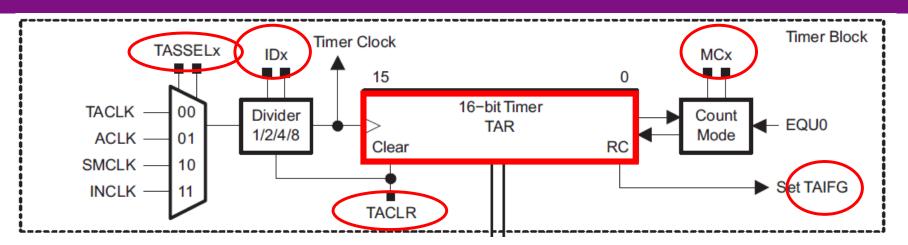

### **Registers in Timer\_A**

- TAR (0170h): the counter itself

- TACCRO (0172h): target for counting

- <u>TACTL</u> (0160h): control settings

- Others: clock source selection, flags

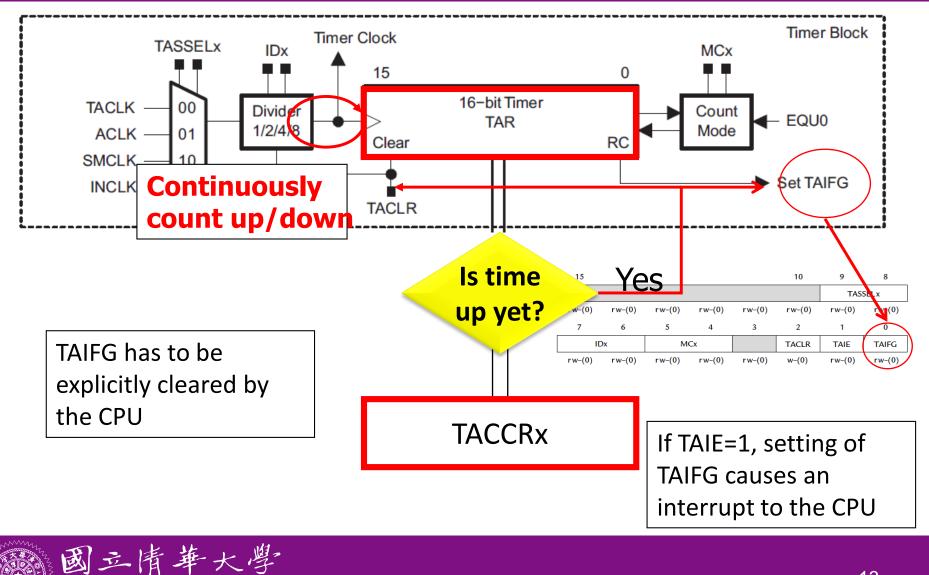

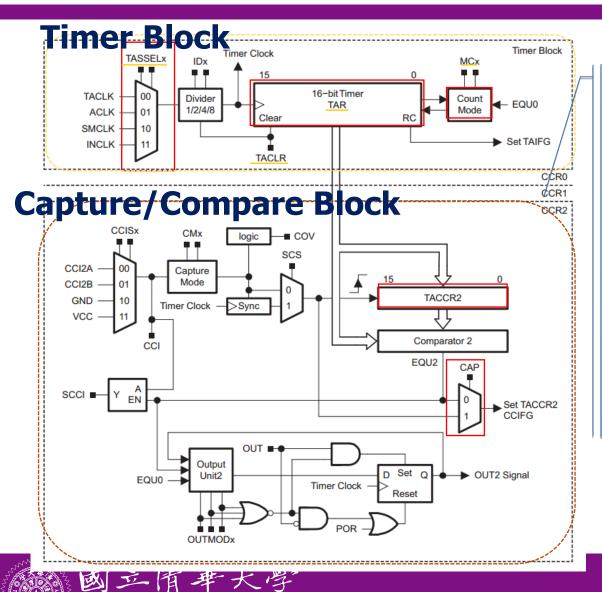

## Inside Timer\_A

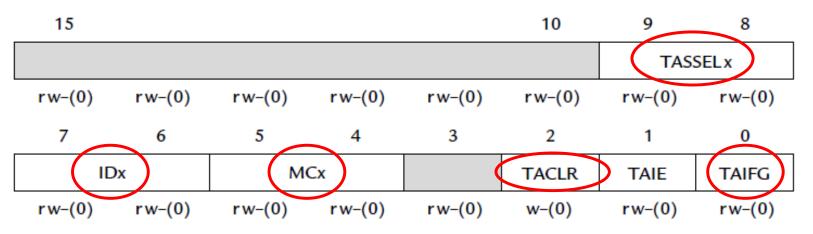

• Timer\_A Control Register: TACTL

# **Typical Operations of Timer\_A**

National Tsing Hua University

## Timer\_A Control Register (TACTL)

- TASSELx: Timer\_A clock source select

- IDx: input divider

- MCx: mode control

- TACLR: Timer\_A clear

- TAIE: Timer\_A interrupt enable

- TAIFG: Timer\_A interrupt flag

| 15     |        |        |        |        | 10     | 9      | 8      |

|--------|--------|--------|--------|--------|--------|--------|--------|

|        |        |        |        |        |        | TAS    | SELx   |

| rw-(0) |

| 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

| ID     | IDx    |        | Cx     |        | TACLR  | TAIE   | TAIFG  |

| rw-(0) | rw-(0) | rw-(0) | rw-(0) | rw-(0) | w-(0)  | rw-(0) | rw-(0) |

#### TACTL, Timer\_A Control Register

|       | 15           | 14         |         | 13               | 12                                        | 11                   | 10                  | 9                 | 8          |

|-------|--------------|------------|---------|------------------|-------------------------------------------|----------------------|---------------------|-------------------|------------|

|       |              |            |         | Unu              | sed                                       |                      |                     | TAS               | SELx       |

|       | rw-(0)       | rw-(0)     |         | rw-(0)           | rw-(0)                                    | rw-(0)               | rw-(0)              | rw-(0)            | rw-(0)     |

|       | 7            | 6          |         | 5                | 4                                         | 3                    | 2                   | 1                 | 0          |

|       | ID           | )x         |         | MC               | Cx .                                      | Unused               | TACLR               | TAIE              | TAIFG      |

|       | rw-(0)       | rw-(0)     |         | rw-(0)           | rw-(0)                                    | rw-(0)               | rw-(0)              | rw-(0)            | rw-(0)     |

|       | Unused       | Bits 15-10 | Unused  | t                |                                           |                      |                     |                   |            |

|       | TASSELX      | Bits 9-8   | Timer_  | A clock source   | select                                    |                      |                     |                   |            |

|       |              |            | 00      | TACLK            |                                           |                      |                     |                   |            |

|       |              |            | 01      | ACLK             |                                           |                      |                     |                   |            |

|       |              |            | 10      | SMCLK            |                                           |                      |                     |                   |            |

|       |              |            | 11      |                  | K is device-speci<br>fic data sheet)      | fic and is often as  | signed to the inver | ted TBCLK) (see   | the        |

|       | IDx          | Bits 7-6   | Input d | ivider. These b  | its select the divid                      | der for the input cl | ock.                |                   |            |

|       |              |            | 00      | /1               |                                           |                      |                     |                   |            |

|       | NL           |            | 01      | /2               |                                           |                      |                     |                   |            |

| 7.    |              |            | 10      | /4               |                                           |                      |                     |                   |            |

| ~     |              | •          | 11      | /8               |                                           |                      |                     |                   |            |

|       | MCx          | Bits 5-4   | Mode of | control. Setting | MCx = 00h when                            | Timer_A is not in    | use conserves po    | wer.              |            |

| 4     |              |            | 00      | Stop mode: t     | he timer is halted                        |                      |                     |                   |            |

|       | $1 \wedge N$ |            | 01      | Up mode: the     | e timer counts up                         | to TACCR0.           |                     |                   |            |

|       |              |            | 10      | Continuous n     | node: the timer co                        | ounts up to OFFFF    | h.                  |                   |            |

|       | Y '          |            | 11      | Up/down mo       | de: the timer cour                        | nts up to TACCR0     | then down to 0000   | Dh.               |            |

|       | Unused       | Bit 3      | Unused  | t                |                                           |                      |                     |                   |            |

|       | TACLR        | Bit 2      |         |                  | g this bit resets T/<br>nd is always read |                      | ler, and the count  | direction. The TA | CLR bit is |

|       | TAIE         | Bit 1      | Timer_  | A interrupt ena  | able. This bit enab                       | les the TAIFG inte   | errupt request.     |                   |            |

|       |              |            | 0       | Interrupt disa   | bled                                      |                      |                     |                   |            |

|       |              |            | 1       | Interrupt ena    | bled                                      |                      |                     |                   |            |

|       | TAIFG        | Bit 0      | Timer_  | A interrupt flag | 1                                         |                      |                     |                   |            |

| MM LZ |              |            | 0       | No interrupt p   | pending                                   |                      |                     |                   |            |

|       | TACTL = TA   | SSEL_2     | + M0    | C_1;             |                                           | // src               | from SM             | ICLK, uj          | o mode     |

National Ising Hua University

## **Timer Mode**

- •MCx=00: Stop mode

- The timer is halted

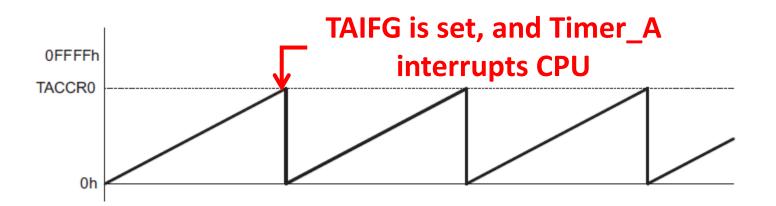

- •MCx=01: Up mode

- The timer repeatedly counts from 0 to TACCR0

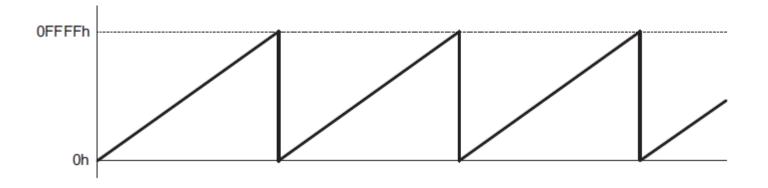

- MCx=10: Continuous mode

- The timer repeatedly counts from 0 to 0FFFFh

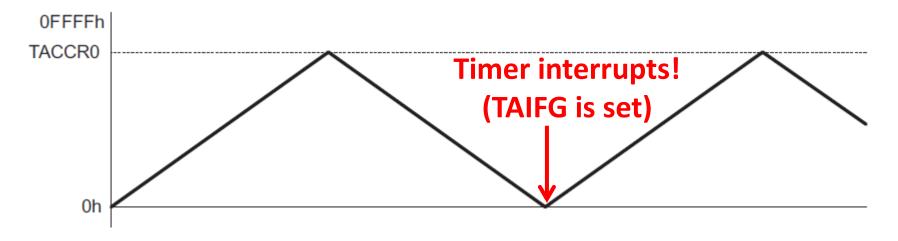

- •MCx=11: Up/down mode

- The timer repeatedly counts from 0 to TACCR0 and back down to 0

The up mode is used if the timer period must be **different** from **OFFFFh** counts.

- 1. Timer period 100  $\rightarrow$  store 99 to TACCR0

- 2. When TACCR0 == 99, set TACCR0 CCIFG interrupt flag

- 3. Reset timer to 0 and set TAIFG interrupt flag

# **Continuous Mode**

- In the continuous mode, the timer repeatedly counts up to 0FFFFh and restarts from zero

- The TAIFG interrupt flag is set when the timer resets from 0FFFFh to zero

# Up/Down Mode

The up/down mode is used if the timer period must be different from 0FFFFh counts, and if a symmetrical pulse generation is needed.

#### $\rightarrow$ The period is twice the value in TACCR0

### Timer\_A Capture/Compare Block

- May contain several Capture/Compare Blocks

- Each Capture/Compare Block is controlled by a control register, TACCTLx

- Inside each

Capture/Compare Block, the Capture/Compare Register, **TACCRx**, holds the count to configure the timer

National Tsing Hua University

#### **Modes of Capture/Compare Block**

- Compare mode:

- Compare the value of TAR with the value stored in TACCRn and update an output when they match

- Capture mode: used to record time events

- Records the "time" (value in TAR) at which the input changes in TACCRx

- The input, usually CCIxA and CCIxB, can be either external or internal from another peripheral or software, depending on board connections

TACCR0 = 24000; // represent 2 sec with 12kHz clk src

#### TACCTLx, Capture/Compare Control Register

| 15      | 14             |       | 13                                | 12                                       | 11                  | 10                    | 9                   | 8                |

|---------|----------------|-------|-----------------------------------|------------------------------------------|---------------------|-----------------------|---------------------|------------------|

|         | СМх            |       | CCISx                             |                                          | SCS                 | SCCI                  | Unused              | CAP              |

| rw-(0)  | rw-(0)         | -     | rw-(0)                            | rw-(0)                                   | rw-(0)              | r                     | rO                  | rw-(0)           |

| 7       | 6              |       | 5                                 | 4                                        | 3                   | 2                     | 1                   | 0                |

| OUTMODx |                |       | CCIE                              | CCI                                      | OUT                 | COV                   | CCIFG               |                  |

| rw-(0)  | rw-(0)         |       | rw-(0)                            | rw-(0)                                   | r                   | rw-(0)                | rw-(0)              | rw-(0)           |

| СМх     | Bit 15-14      | Captu | ire mode                          |                                          |                     |                       |                     |                  |

|         |                | 00    | No capture                        |                                          |                     |                       |                     |                  |

|         |                | 01    | Capture on                        | rising edge                              |                     |                       |                     |                  |

|         |                | 10    | Capture on                        | falling edge                             |                     |                       |                     |                  |

|         |                | 11    | Capture on                        | both rising and fal                      | ling edges          |                       |                     |                  |

| CCISx   | Bit 13-12      |       |                                   | put select. These b<br>gnal connections. | oits select the TAC | CCRx input signal.    | See the device-sp   | ecific data      |

|         |                | 00    | CCIxA                             |                                          |                     |                       |                     |                  |

|         |                | 01    | CCIxB                             |                                          |                     |                       |                     |                  |

|         |                | 10    | GND                               |                                          |                     |                       |                     |                  |

|         |                | 11    | V <sub>cc</sub>                   |                                          |                     |                       |                     |                  |

| SCS     | Bit 11         | Synch | hronize capture                   | e source. This bit is                    | s used to synchror  | nize the capture inp  | out signal with the | timer clock.     |

|         |                | 0     | Asynchron                         | ous capture                              |                     |                       |                     |                  |

|         |                | 1     | Synchrono                         | us capture                               |                     |                       |                     |                  |

| SCCI    | Bit 10         |       | hronized captu<br>ad via this bit | re/compare input.                        | The selected CCI    | input signal is latch | ned with the EQU    | x signal and can |

| Unused  | Bit 9          | Unus  | ed. Read only.                    | Always read as 0.                        |                     |                       |                     |                  |

|         | tional Tsing F | lua U | niversity                         |                                          |                     |                       |                     | 22               |

#### TACCTL cont'd

| САР         | Bit 8        | Capture mode                                                                                              |

|-------------|--------------|-----------------------------------------------------------------------------------------------------------|

|             |              | 0 Compare mode                                                                                            |

|             |              | 1 Capture mode                                                                                            |

| OUTMODx     | Bits 7-5     | Output mode. Modes 2, 3, 6, and 7 are not useful for TACCR0, because EQUx = EQU0.                         |

|             |              | 000 OUT bit value                                                                                         |

|             |              | 001 Set                                                                                                   |

|             |              | 010 Toggle/reset                                                                                          |

|             |              | 011 Set/reset                                                                                             |

|             |              | 100 Toggle                                                                                                |

|             |              | 101 Reset                                                                                                 |

|             |              | 110 Toggle/set                                                                                            |

|             |              | 111 Reset/set                                                                                             |

| CCIE        | Bit 4        | Capture/compare interrupt enable. This bit enables the interrupt request of the corresponding CCIFG flag. |

|             |              | 0 Interrupt disabled                                                                                      |

|             |              | 1 Interrupt enabled                                                                                       |

| CCI         | Bit 3        | Capture/compare input. The selected input signal can be read by this bit.                                 |

| OUT         | Bit 2        | Output. For output mode 0, this bit directly controls the state of the output.                            |

|             |              | 0 Output low                                                                                              |

|             |              | 1 Output high                                                                                             |

| cov         | Bit 1        | Capture overflow. This bit indicates a capture overflow occurred. COV must be reset with software.        |

|             |              | 0 No capture overflow occurred                                                                            |

|             |              | 1 Capture overflow occurred                                                                               |

| CCIFG       | Bit 0        | Capture/compare interrupt flag                                                                            |

|             |              | 0 No interrupt pending                                                                                    |

|             |              | 1 Interrupt pending                                                                                       |

| Z WAUNES NO | tional Ising | Hua University                                                                                            |

### Sample Code 1 for Timer\_A

- Goal: simplest way to flash an LED at 1 Hz

- Need an event to trigger the flashing

- $\rightarrow$  counter (TAR) overflow

- Need a way to detect the event

- $\rightarrow$  CPU polling

- How to make TAR overflow at 1 Hz?

- Use SMCLK clock (discussed later) at 800 KHz

- When TAR (16 bits) overflows, it has counted 2<sup>16</sup>, equivalent to a period of 2<sup>16</sup>/800KHz ≈ 0.08 sec

- Divide the frequency of the clock by 8 to give a period of about 0.66 sec → close enough!

- Continuously count up; on overflow return to 0

#### Sample Code 1 for Timer\_A

```

#define LED1 BIT0

void main(void) {

WDTCTL = WDTPW | WDTHOLD; // Stop watchdog timer

P1OUT = \approx LED1;

P1DIR = LED1;

TACTL = MC 2|ID 3|TASSEL 2|TACLR; //Setup Timer A

for (;;) { // Loop forever

while (TACTL bit.TAIFG == 0) { // Wait overflow

} // CPU polling and doing nothing

TACTL bit.TAIFG = 0; // Clear overflow flag

P1OUT ^= LED1; // Toggle LEDs

} // Back around infinite loop

```

### **Sample Code Settings Explained**

The following symbols are defined in header file:

- MC\_2: set MC of TACTL to 10 (continuous mode)

- ID\_3: set ID of TACTL to 11 (divide freq. by 8)

- TASSEL\_2: set TASSEL to 10 (use SMCLK)

- TACLR: clear the counter, the divider, and the direction of the count

#### Sample Code 2 for Timer\_A

- Can have more accurate time if we can control the amount to count

- The maximum desired value of the count is programmed into TACCR0

- TAR starts from 0 and counts up to the value in TACCR0, after which it returns to 0 and sets TAIFG

- Thus the period is TACCR0+1 counts

- With SMCLK (800KHz) divided down to 100 KHz, we need 50,000 counts for a delay of 0.5 sec → store 49,999 in TACCR0

```

TACCR0 = 49999; // Upper limit of count for TAR

TACTL = MC_1 | ID_3 | TASSEL_2 | TACLR; // Set up and start Timer A

// "Up to CCR0" mode, divide clock by 8, clock from SMCLK, clear timer

```

- Basic concepts of timers

- MSP430 timers

- An example of using MSP430 Timer\_A

- Clocks in MSP430

#### Theoretically, One Clock Is Enough

- A clock is a square wave signal whose edges trigger hardware

- A clock source, e.g. crystal, to drive CPU directly, which is divided down by a factor of 2 or 4 for the main bus and rest of circuit board

- But, systems have conflicting requirements

- Low power, fast start/stop, accuracy

### **Different Requirements for Clocks**

• Devices often in a low-power mode until some event occurs, then must wake up and handle event rapidly

Clock must get to be stabilized quickly

- Devices also need to keep track of real time: (1) can wake up periodically, or (2) time-stamp external events

- Therefore, two kinds of clocks often needed:

- A fast clock to drive CPU, which can be started and stopped rapidly but need not be particularly accurate

- A slow clock that runs continuously to monitor real time, which must use little power and be accurate

#### **Different Requirements for Clocks**

- Different clock sources also have different characteristics

- Crystal: accurate and stable (w.r.t. temperature or time); expensive, delicate, drawing large current, external component, longer time to start up/stabilize

- Resistor and capacitor (RC): cheap, quick to start, integrated within MCU and sleep with CPU; poor accuracy and stability

- Ceramic resonator and MEMS clocks in between

#### Need multiple clocks

## **Clocks in MSP430**

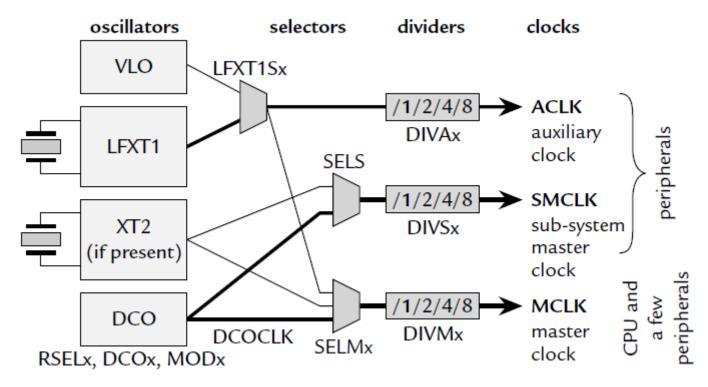

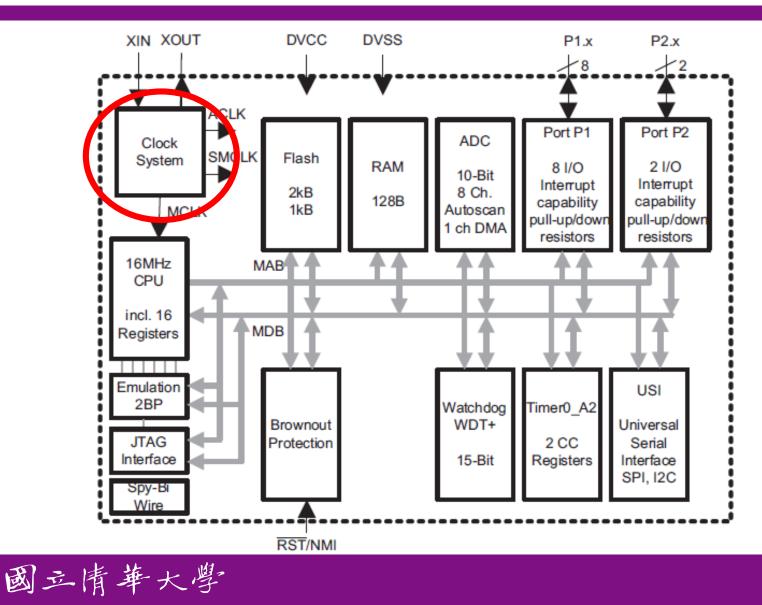

- MSP430 addresses the conflicting demands for high performance, low power, precise frequency by using 3 internal clocks, which can be derived from up to 4 sources

- Master clock (MCLK): for CPU & some peripherals, normally driven by *digitally controlled oscillator* (DCO)

- Subsystem master clock (SMCLK): distributed to peripherals, normally driven by DCO

- Auxiliary clock (ACLK): distributed to peripherals, normally for real-time clocking, normally driven by a low-frequency crystal oscillator, typically at 32 KHz

# **Clock Sources**

- Low- or high-frequency crystal oscillator, LFXT1:

- External; used with a low- or high frequency crystal; an external clock signal can also be used; connected to MSP430 through XIN and XOUT pins

- High-frequency crystal oscillator, XT2:

- External; similar to LFXT1 but at high frequencies

- Very low-power, low-frequency oscillator, VLO:

- Internal at 12 KHz; alternative to LFXT1 when accuracy of a crystal is not needed; may not available in all devices

- Digitally controlled oscillator, DCO:

- Internal; a highly controllable RC oscillator that starts fast

### **From Sources to Clocks**

- Typical sources of clocks:

- MCLK, SMCLK: DCO (typically at 1.1 MHz)

- ACLK: LFXT 1 (typically at 32 KHz)

#### **MSP430 Clock System**

National Tsing Hua University

## **Controlling Clocks**

- In MSP430, the Basic Clock Module is also an IO peripheral

- Being an IO peripheral, it can be controlled by registers, DCOCTL and BCSCTL1–3

- DCOCTL (056h): configure DCO

- BCSCTL1 (basic clock system control 1, 057h): configure ACLK

- BCSCTL2 (basic clock system control 2, 058h): configure MCLK, SMCLK

- BCSCTL3 (basic clock system control 3, 053h): control LFXT1/VLO

## **Control Registers for Clocks**

#### Control Registers for Clock System Table 5-1. Basic Clock Module+ Registers

| Register                        | Short Form | Register Type | Address | Initial State                |

|---------------------------------|------------|---------------|---------|------------------------------|

| DCO control register            | DCOCTL     | Read/write    | 056h    | 060h with PUC                |

| Basic clock system control 1    | BCSCTL1    | Read/write    | 057h    | 087h with POR <sup>(1)</sup> |

| Basic clock system control 2    | BCSCTL2    | Read/write    | 058h    | Reset with PUC               |

| Basic clock system control 3    | BCSCTL3    | Read/write    | 053h    | 005h with PUC <sup>(2)</sup> |

| SFR interrupt enable register 1 | IE1        | Read/write    | 000h    | Reset with PUC               |

| SFR interrupt flag register 1   | IFG1       | Read/write    | 002h    | Reset with PUC               |

Some of the register bits are also PUC initialized (see Section 5.3.2).

The initial state of BCSCTL3 is 000h in the MSP430AFE2xx devices.

DCOCTL and BCSCTL1 combined define the frequency of DCO, among other settings

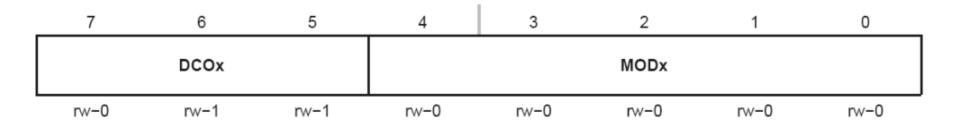

## DCOCTL (at Memory Address 056h)

#### DCOCTL, DCO Control Register

DCOx

Bits

DCO frequency select.

These bits select which of the eight discrete DCO

7-5

frequencies of the RSELx setting is selected.

MODx

Bits

Modulator selection.

These bits define how often the f<sub>DCO+1</sub> frequency is

4-0 used within a period of 32 DCOCLK cycles. During the remaining clock cycles (32–M Tag-Length-Value used. Not useable when DCOx=7.

$DCOCTL = CALDCO_1MHZ;$

// Set DCO step + modulation

Tag-Length-Value (TLV) stores device-specific information in the flash memory to set DCOCTL and BCSCTL1 for DCO frequency

| Label        | Description                                                    | Offset |

|--------------|----------------------------------------------------------------|--------|

| CALBC1_1MHZ  | Value for the BCSCTL1 register for 1 MHz, $T_A = 25^{\circ}C$  | 0x07   |

| CALDCO_1MHZ  | Value for the DCOCTL register for 1 MHz, $T_A = 25^{\circ}C$   | 0x06   |

| CALBC1_8MHZ  | Value for the BCSCTL1 register for 8 MHz, $T_A = 25^{\circ}C$  | 0x05   |

| CALDCO_8MHZ  | Value for the DCOCTL register for 8 MHz, $T_A = 25^{\circ}C$   | 0x04   |

| CALBC1_12MHZ | Value for the BCSCTL1 register for 12 MHz, $T_A = 25^{\circ}C$ | 0x03   |

| CALDCO_12MHZ | Value for the DCOCTL register for 12 MHz, $T_A = 25^{\circ}C$  | 0x02   |

| CALBC1_16MHZ | Value for the BCSCTL1 register for 16 MHz, $T_A = 25^{\circ}C$ | 0x01   |

| CALDCO_16MHZ | Value for the DCOCTL register for 16 MHz, $T_A = 25^{\circ}C$  | 0x00   |

#### **DCO Calibration Data (Device Specific)**

BCSCTL1 = CALBC1\_1MHZ;

// Set range

DCOCTL = CALDCO\_1MHZ;

#### BCSCTL1, Basic Clock System Control Register 1

| 7      | 6                     |                                                                                                                                                            | 5                   | 4                                             | 3     | 2    | 1    | 0              |  |  |

|--------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------------------------------|-------|------|------|----------------|--|--|

| XT2OFF | XTS <sup>(1)(2)</sup> |                                                                                                                                                            | DIVAx               |                                               | RSELx |      |      |                |  |  |

| rw-(1) | rw-(0)                |                                                                                                                                                            | rw-(0)              | rw-(0)                                        | rw-0  | rw-1 | rw-1 | rw-1           |  |  |

| XT2OFF | Bit 7                 | XT2 o                                                                                                                                                      | off. This bit turns | s off the XT2 oscill                          | ator  |      |      |                |  |  |

|        |                       | 0 XT2 is on                                                                                                                                                |                     |                                               |       |      |      |                |  |  |

|        |                       | 1                                                                                                                                                          | XT2 is off if i     | 2 is off if it is not used for MCLK or SMCLK. |       |      |      |                |  |  |

| XTS    | Bit 6                 | LFXT                                                                                                                                                       | 1 mode select.      |                                               |       |      |      |                |  |  |

|        |                       | 0 Low-frequency mode                                                                                                                                       |                     |                                               |       |      |      |                |  |  |

|        |                       | 1                                                                                                                                                          | High-frequer        | ncy mode                                      |       |      |      |                |  |  |

| DIVAx  | Bits 5-4              | Divide                                                                                                                                                     | er for ACLK         |                                               |       |      |      |                |  |  |

|        |                       | 00                                                                                                                                                         | /1                  |                                               |       |      |      |                |  |  |

|        |                       | 01                                                                                                                                                         | /2                  |                                               |       |      |      |                |  |  |

|        |                       | 10 /4                                                                                                                                                      |                     |                                               |       |      |      |                |  |  |

|        |                       | 11                                                                                                                                                         | /8                  |                                               |       |      |      |                |  |  |

| RSELx  | Bits 3-0              | Range select. Sixteen different frequency ranges are available. The lowest frequency range is selected by setting RSELx=0. RSEL3 is ignored when DCOR = 1. |                     |                                               |       |      |      | is selected by |  |  |

#### BCSCTL1 = CALBC1 1MHZ;

// Set range

BCSCTL2

National Tsing Hua University

BCSCTL2, Basic Clock System Control Register 2 **SMCLK** MCLK 0 DCOR<sup>(1)(2)</sup> SELMx DIVMx DIVSx SELS rw-0 rw-0 rw-0 rw-0 rw-0 rw-0 rw-0 rw-0 SELMx Select MCLK. These bits select the MCLK source. Bits 7-6 00 DCOCLK DCOCLK 01 XT2CLK when XT2 oscillator present on-chip. LFXT1CLK or VLOCLK when XT2 oscillator not 10 present on-chip. 11 LFXT1CLK or VLOCLK **DIVMx** Bits 5-4 Divider for MCLK 00 /1 /2 01 14 10 11 /8 SELS Bit 3 Select SMCLK. This bit selects the SMCLK source. DCOCLK 0 1 XT2CLK when XT2 oscillator present. LFXT1CLK or VLOCLK when XT2 oscillator not present DIVSx Bits 2-1 Divider for SMCLK 00 /1 BCSCTL2 SELM 3 + DIVM 3; MCLK = VLO/8// = /8 11 國立清華大學

BCSCTL3

National Tsing Hua University

In MSP430G2231 7 0 6 з XT2OF<sup>(2)</sup> XT2Sx LFXT1Sx XCAPx<sup>(1)</sup> LFXT1OF<sup>(1)</sup> rw-0 rw-0 rw-0 rw-1 r0 r-(1) Bits 7-6 XT2 range select. These bits select the frequency range for XT2. XT2Sx 0.4- to 1-MHz crystal or resonator 00 01 1- to 3-MHz crystal or resonator 10 3- to 16-MHz crystal or resonator 11 Digital external 0.4- to 16-MHz clock source LFXT1Sx Bits 5-4 Low-frequency clock select and LFXT1 range select. These bits select between LFXT1 and VLO when XTS = 0, and select the frequency range for LFXT1 when XTS = 1. When XTS = 0: 00 32768-Hz crystal on LFXT1 01 Reserved 10 VLOCLK (Reserved in MSP430x21x1 devices) 11 Digital external clock source When XTS = 1 (Not applicable for MSP430x20xx devices) 00 0.4- to 1-MHz crystal or resonator 01 1- to 3-MHz crystal or resonator 10 3- to 16-MHz crystal or resonator BCSCTL3 // Enable VLO as MCLK/ACLK src = LFXT1S 01 Reserved 40 VILOOL IZ 國立清華大學

#### BCSCTL3, Basic Clock System Control Register 3

#### Interrupt Flag Register 1 (IFG1)

• OFIFG oscillator-fault flag is set when an oscillator fault (LFXT1OF) is detected.

#### IFG1, Interrupt Flag Register 1

| 7     | 6           | 5                                                                                                                                                                                                                 | 4 | 3 | 2 | 1     | 0 |  |  |

|-------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|-------|---|--|--|

|       |             |                                                                                                                                                                                                                   |   |   |   | OFIFG |   |  |  |

|       |             |                                                                                                                                                                                                                   |   |   |   | rw-1  |   |  |  |

|       | Bits 7-2 Th | These bits may be used by other modules. See device-specific data sheet.                                                                                                                                          |   |   |   |       |   |  |  |

| OFIFG |             | Oscillator fault interrupt flag. Because other bits in IFG1 may be used for other modules, it is recommended to set or clear this bit using BIS.B or BIC.B instructions, rather than MOV.B or CLR.B instructions. |   |   |   |       |   |  |  |

|       | 0           | 0 No interrupt pending                                                                                                                                                                                            |   |   |   |       |   |  |  |

|       | 1           | 1 Interrupt pending                                                                                                                                                                                               |   |   |   |       |   |  |  |

|       | Bits 0 Th   | This bit may be used by other modules. See device-specific data sheet.                                                                                                                                            |   |   |   |       |   |  |  |

|       |             |                                                                                                                                                                                                                   |   |   |   |       |   |  |  |

IFG1 &= ~OFIFG;

// Clear OSCFault flag

### **Recall Sample Code for Timer\_A**

#### • Flash red LED at 1 Hz if SMCLK at 800 KHz

```

#include <msp430g2553.h>

#define LED1 BIT0

void main (void) {

WDTCTL = WDTPW | WDTHOLD; // Stop watchdog timer

P1OUT = \sim LED1;

P1DIR = LED1;

TACCR0 = 49999;

TACTL = MC 1 | ID 3 | TASSEL 2 | TACLR; //Setup Timer A

//up mode, divide clk by 8, use SMCLK, clr timer

for (;;) { // Loop forever

while (!(TACTL&TAIFG)) { // Wait time up

} // doing nothing

TACTL &= ~TAIFG; // Clear overflow flag

P1OUT ^= LED1; // Toggle LEDs

} // Back around infinite loop

```

## **Sample Code for Setting Clocks**

• Set DCO to 1MHz, enable crystal

```

#include <msp430g2231.h> (#include <msp430g2553.h> )

void main(void) {

WDTCTL = WDTPW + WDTHOLD; // Stop watchdog timer

if (CALBC1 1MHZ == 0 \times FF || CALDCO 1MHZ == 0 \times FF)

while(1); // If TLV erased, TRAP!

BCSCTL1 = CALBC1 1MHZ; // Set range

DCOCTL = CALDCO 1MHZ;

P1DIR = 0x41; // P1.0 \& 6 outputs (red/green LEDs)

P1OUT = 0x01; // red LED on

BCSCTL3 |= LFXT1S 0; // Enable 32768 crystal

IFG1 &= ~OFIFG;// Clear OSCFault flag

P1OUT = 0; // red LED off

BCSCTL2 |= SELS 0 + DIVS 3; // SMCLK = DCO/8

// infinite loop to flash LEDs

```

國立情華大学 National Tsing Hua University